How Silicon Wafer Quality Parameters Affect the Performance of Semiconductor Devices

Introduction

The semiconductor industry is expanding worldwide, driven by rapid tech innovation in 5G, artificial intelligence (AI), and electric vehicles. The World Semiconductor Trade Statistics (WSTS) estimated the global semiconductor market at a record $574 billion in 2022, an increase of 3.3% year-over-year. As the bedrock of chip manufacturing, silicon wafers are poised to advance at breakneck speeds with this growth.

Silicon wafers are the initial substrate material of integrated circuits. The quality of the crystal, surface condition, and dimensional tolerance directly impact important device parameters, including electron mobility, power dissipation, and reliability. Dislocations, grain boundaries, and impurities can degrade performance and shorten device life. Also, improper wafer thickness or warpage can cause stress-related failures during processing. Now let us go about discovering the basic quality factors of silicon wafers and how they affect the performance of semiconductor devices.

![]()

Major Factors Affecting the Quality of Silicon Wafers

--Crystal Structure: Purity and Defects

Silicon wafer electrical performance is highly impurity-sensitive. Industrial silicon can achieve 99.9% purity but semiconductor-grade wafers demand ultra-high purity of 99.999999999% (11N). That high degree of purification is necessary in order to achieve low defect density and high carrier mobility in future microelectronics.

Even in extremely pure monocrystalline silicon, the lattice arrangement can fail to be the perfect periodic structure, hence yielding crystallographic defects:

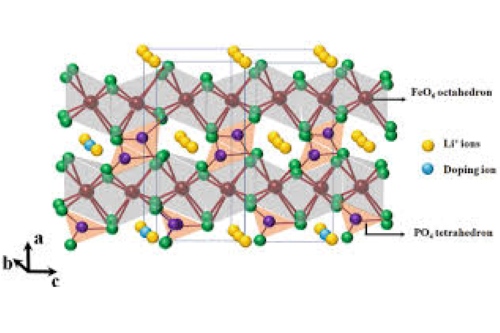

•Dislocations: Line defects in which the atoms are out of place from their equilibium sites. Dislocations result in local electronic disruptions, reduce carrier mobility, and increase charge carrier recombination rates.

•Stacking faults and vacancies: Atomic-scale flaws that can propagate under thermal cycling and result in device leakage current and parametric drift.

•Grain boundaries (in multicrystalline wafers): These can trap charge carriers, reduce carrier lifetimes, and hinder current flow.

Further reading: Essential Electronic Materials: Part 1 - Silicon

--Surface Quality: Flatness, Roughness, and Contamination

The surface condition of a silicon wafer is very important during photolithography, etching, deposition, and planarization:

• Flatness: Measured in terms of Total Thickness Variation (TTV) and Site Flatness (SFQR), flatness affects the uniformity of photoresist application and precision of alignment. High-end processes require TTV < 0.5 µm for 300 mm wafers.

•Surface Roughness: Typically needs to be < 0.2 nm RMS for front-side polished wafers. Increased roughness causes scattering loss and pattern distortion.

•Contamination: Particles of diameter >0.3 µm, organic deposit, and metal impurities (e.g., Fe, Cu, Na) have the potential to produce fatal defects. Density of particles is controlled below 0.3 particles/cm² in ultra-clean wafers. Contaminants are introduced by cutting, polishing, or airborne path.

--Dimensional Accuracy: Diameter, Thickness, and Warpage

With increasing chip complexity, silicon wafers must meet increasingly tighter geometrical tolerances:

•Wafer Diameter: Standard diameters include 150 mm, 200 mm, and 300 mm. A 300 mm wafer yields 2.25× more chips than a 200 mm wafer, increasing cost-effectiveness.

•Wafer Thickness: Thickness must be sufficient so as not to crack during processing. An example is a 300 mm wafer with a typical thickness of 775 µm.

•Warpage: Severe warpage (bow and warp >50 µm) causes lithographic misalignment and non-planar film deposition. Warpage is minimized by refining crystal pulling rates and thermal stress profiles during wafer manufacturing.

How Silicon Wafer Quality Parameters Affect Semiconductor Device Performance

--Crystal Structure and Lattice Defects

Crystal structure defects are among the most debilitating limitations in device performance:

•Elevated Resistivity: Dislocations act as scattering centers, impeding electron mobility and increasing resistivity.

•Carrier Concentration Changes: Dislocation stress fields cause local band structure modifications, affecting doping activation and carrier creation.

•Decreased Carrier Lifetimes: Dislocation-created recombination sites drastically reduce minority carrier lifetimes, impairing switching speed in transistors.

•Reduced Electron Mobility: High defect density reduces electron mobility, creating slower logic gates and impaired analog performance.

--Surface Flatness

Flatness at the surface impacts a variety of device characteristics:

•Contact Resistance: Non-planar surfaces induce contact resistances in metal-semiconductor contacts and create performance variability.

•Photolithography Accuracy: Focus and exposure issues on non-planar wafers induce pattern deformation or overlay errors.

•Etching and Deposition Quality: Flatness deficiency results in uneven etch rates and film thickness variations, leading to hotspots or open circuits.

--Grain Boundaries and Impurities

Trace impurities may lead to serious electronic degradation:

• Resistivity Fluctuation: Phosphorus doping in the range of 10²¹ and 10¹² atoms/cm³ shifts resistivity between 10⁻⁴ and 10⁴ Ω·cm, a ten-million-fold fluctuation.

• Carrier Scattering: Impurities such as Fe, Cu, or Mg create local recombination centers and trapping states.

• Breakdown Hazard: In high-voltage devices, impurities lead to premature breakdown due to localized field enhancement.

Conclusion

The performance and reliability of semiconductor devices are tightly coupled to the intrinsic quality of the silicon wafers they are built upon.

Key quality parameters—such as crystal purity, structural defects, surface flatness, contamination levels, and dimensional precision—each play a crucial role in defining the wafer’s electrical behavior and its compatibility with advanced fabrication processes. Dislocations and impurities diminish carrier mobility and lifetime, surface roughness disrupts lithographic precision, and warpage undermines mechanical stability.

As the semiconductor industry races forward with innovations in AI, 5G, and automotive electronics, maintaining strict control over silicon wafer quality is more important than ever. Investing in high-purity materials, advanced crystal growth, and meticulous surface processing is not just about meeting specs—it’s essential to enabling the next generation of fast, efficient, and reliable semiconductor devices. For more information, please check Stanford Electronics.